Projects

採択課題

研究成果最適展開支援プログラム A-STEP ステージⅡ(シーズ育成タイプ)平成29年度採択課題<AS2915017R>「IoT時代の高信頼VLSIシステムの開発」

研究概要

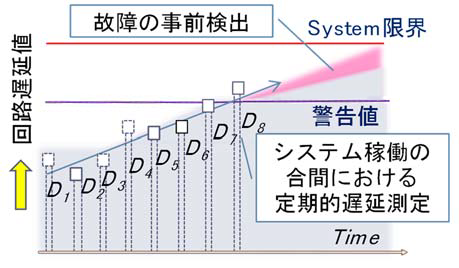

VLSIの劣化自動車分野(特に自動運転)に代表される次世代システムの開発や社会課題、企業内課題解決のためのIoTソリューションにおいて、システム高信頼化のためのVLSIの性能モニタリングとして利用される。構成部品のVLSIの故障予知が可能になることは、システムの信頼性を高め、新規の技術開発やサービス導入を促進し、IoT市場、自動車電子部品市場へ大きなインパクトがある。研究開発を通じて、IoTや高信頼化システム向けIP提供サービス、受託設計サービス及び、VLSIの設計コンサルティングサービスの実現を目指す。本課題で扱う技術は、環境補正を伴う遅延測定に基づく劣化検知技術[出願特許1]とリング発振器を用いたデジタル温度電圧センサ技術[出願特許2]を用いたフィールドテスト向けの劣化検知技術(DART※)であり、そのシステム化・実用化における課題解決、および、実回路を利用したシステムの構築と検証を行う。

※DART技術(Dependable Architecture with Reliability Testing)

遅延マージン低下の事前検知と故障の事前回避を可能とするフィールド向けのオンチップ劣化検知システム。運用時の空き時間(パワーオン・オフ時など)にVLSIの自己テストを行い、CUT(被測定回路)の遅延値の測定及び以前時刻と比較することで劣化量を算出する。同時にチップ上の温度電圧測定を行うことでテスト時の環境影響の補正を行う。

図1 DART遅延測定による劣化検知 図2 DART遅延測定のリアルタイム可視化

(赤:温度,青:遅延値,緑:環境補正後)

[参考文献2] Yousuke Miyake, Yasuo Sato, Seiji Kajihara, and Yukiya Miura, "Temperature and Voltage Measurement for Field Test Using an Aging-Tolerant Monitor," IEEE Transactions on Very Large Scale Integration Systems, Vol. 24, No. 11, pp. 3282-3295, Nov. 2016. DOI:10.1109/TVLSI.2016.2540654

実施期間

2017年10月1日~2021年9月30日共同研究

産学連携:九州工業大学、株式会社プリバテック、東京都立大学

企業責任者 株式会社プリバテック

研究責任者 梶原 誠司 九州工業大学

研究業績

以下、計41件(2021年9月時点)オープンアクセス可能な論文はDOIリンク先でご覧ください(外部リンク:九州工業大学学術機関リポジトリ)

著書

[1] S. Asai (ed.), S. Kajihara, et al., VLSI Design and Test for Systems Dependability, Springer Japan, ISBN:9784431568636, 2019.査読付き学術論文

[2] Takaaki Kato, Senling Wang, Yasuo Sato, Seiji Kajihara, Xiaoqing Wen, "A Flexible Scan-in Power Control Method in Logic BIST and Its Evaluation with TEG Chips," IEEE Transactions on Emerging Topics in Computing, Volume: 8, Issue: 3, pp. 591 - 601, July-Sept. 1 2020, (Date of Publication: Oct. 2017), DOI:10.1109/TETC.2017.2767070[3] Poki Chen, Jian-Ting Lan, Ruei-Ting Wang, Nguyen My Qui, John Carl Joel S. Marquez, Seiji Kajihara, Yousuke Miyake, "High-Precision PLL Delay Matrix With Overclocking and Double Data Rate for Accurate FPGA Time-to-Digital Converters," IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 28, no. 4, pp. 904-913, April 2020. doi: 10.1109/TVLSI.2019.2962606

査読付き国際会議

[4] Takeru Nishimi, Yasuo Sato, Seiji Kajihara, Yoshiyuki Nakamura, "Good Die Prediction Modelling from Limited Test Items," Proc. IEEE International Test Conference in Asia, Aug. 2018. DOI:10.1109/ITC-Asia.2018.00030[5] Shigeyuki Oshima, Takaaki Kato, Senling Wang, Yasuo Sato and Seiji Kajihara, “On Flip-Flop Selection for Multi-Cycle Scan Test with Partial Observation in Logic BIST," Proc. of IEEE Asian Test Symp., pp. 30-35, Oct. 2018. DOI: 10.1109/ATS.2018.00017

[6] Yousuke Miyake, Yasuo Sato, and Seiji Kajihara, "On-Chip Delay Measurement for In-field Periodic Test of FPGAs," Digest of IEEE International Workshop on Automotive Reliability & Test, P01, pp. 1-6, Nov. 2018.

[7] Shoi Tachibana, Shunsuke Araki, Seiji Kajihara, Shigeyuki Azuchi, Yukishige Nakajo, Hideki Shoda, "FPGA implementation of ECDSA for Blockchain," Proc. of IEEE International Conference on Consumer Electronics - Taiwan (ICCE-TW), 2 pages, May 2019.DOI: 10.1109/ICCE-TW46550.2019.8991918

[8] Yousuke Miyake, Yasuo Sato, and Seiji Kajihara, "A Selection Method of Ring Oscillators for An On-chip Digital Temperature and Voltage Sensor," Proc. IEEE International Test Conference in Asia, pp. 13-18, Sep. 2019. DOI:10.1109/ITC-Asia.2019.00016

[9] Yousuke Miyake, Seiji Kajihara, and Poki Chen, "On-Chip Test Clock Validation Using A Time-to-Digital Converter in FPGAs," Proc. IEEE International Test Conference in Asia, pp. 157-162, Sep. 2019. DOI:10.1109/ITC-Asia.2019.00040

[10] Yousuke Miyake, Yasuo Sato, and Seiji Kajihara, "On-Chip Delay Measurement for In-Field Test of FPGAs," Proc. IEEE Pacific Rim International Symposium on Dependable Computing (PRDC), pp. 130-137, Dec. 2019. DOI:10.1109/PRDC47002.2019.00043

[11] Takeshi Iwasaki, Masao Aso, Haruji Futami, Satoshi Matsunaga, Yousuke Miyake, Takaaki Kato, Seiji Kajihara, Yukiya Miura, Smith Lai, Gavin Hung, Harry H. Chen, Haruo Kobayashi, Kazumi Hatayama, "Innovative Test Practices in Asia," Proc. IEEE VLSI Test Symposium, April 5-8, 2020. DOI: 10.1109/VTS48691.2020.9107640

[12] Yousuke Miyake, Takaaki Kato, Seiji Kajihara, Masao Aso, Haruji Futami, Satoshi Matsunaga, Yukiya Miura, “On-Chip Delay Measurement for Degradation Detection And Its Evaluation under Accelerated Life Test," Proc. IEEE International Symposium on On-Line Testing and Robust System Design (IOLTS), pp. 1-6, July 2020. DOI:10.1109/IOLTS50870.2020.9159717

[13] Yousuke Miyake, Takaaki Kato, and Seiji Kajihara, “Path Delay Measurement with Correction for Temperature And Voltage Variations," Proc. IEEE International Test Conference in Asia, pp.112-117, Sep. 2020. DOI:10.1109/ITC-Asia51099.2020.00031

[14] Masayuki Gondo, Yousuke Miyake, Takaaki Kato, and Seiji Kajihara, “On Evaluation for Aging-Tolerant Ring Oscillators with Accelerated Life Test and Its Application to Digital Sensor," Proc. IEEE Asian Test Symposium, pp. 1-6, Nov. 2020. DOI:10.1109/ATS49688.2020.9301588

国内外研究会等

[15] 大島繁之, 加藤隆明, 王森レイ, 佐藤康夫, 梶原誠司, "スキャンベース論理BISTにおけるマルチサイクルテストの中間観測FF選出手法について," 電子情報通信学会技術研究報告, vol. 117, no. 274, DC2017-47, pp. 85-90, 2017年11月.[16] 三宅庸資, 佐藤康夫, 梶原誠司, "FPGAの自己テストのためのTDCを用いたテストクロック観測手法の検討," 電子情報通信学会技術研究報告, vol. 117, no. 359, DC2017-75, pp. 37-42, 2017-12.

[17] 西見武, 梶原誠司, 中村芳行, "特定のテスト項目を用いた良品予測モデル作成," 第78回FTC研究会,2018年1月.

[18] 井上賢二, 三宅庸資, 梶原誠司, "デジタル温度電圧センサにおける特定温度電圧領域の推定精度向上手法," 電子情報通信学会技術研究報告, vol. 117, no. 444, DC2017-85, pp. 49-54,2018-02.

[19] 波多江雅貴, 三宅庸資, 加藤隆明, 佐藤康夫, 梶原誠司, "デジタル温度電圧センサの精度向上のための推定式の拡充について," 電子情報通信学会2018年総合大会講演論文集, D-10-5, p. 124, 2018-03.

[20] 三宅庸資, 梶原誠司, "FPGAにおける自己補正可能なオンチップデジタル温度センサ," 第17回情報科学技術フォーラム講演論文集(FIT2018), C-010, pp.179-180, 2018-09.

[21] 加藤隆明, 王森レイ, 佐藤康夫, 梶原誠司, "論理BISTのテスト電力制御手法とTEG評価," 電子情報通信学会技術研究報告, vol. 118, no. 335, DC2018-43, pp. 125-130, 2018年12月.

[22] 三宅庸資, 佐藤康夫, 梶原誠司, "FPGAにおける周期的なフィールドテストのためのオンチップ遅延測定," 電子情報通信学会技術研究報告, vol. 118, no. 364, DC2018-58, pp. 1-6, 2018-12.

[23] 古川大悟, 三宅庸資, 梶原誠司, Poki Chen, "FPGAにおけるオンチップ可変テストクロック生成器の検討," 第80回FTC研究会, 2019-01.

[24] 三宅庸資, 加藤隆明, 梶原誠司, 麻生正雄, 二見治司, 松永恵士, 三浦幸也, "長期信頼性試験におけるオンチップ遅延測定による劣化観測," 電子情報通信学会技術研究報告, vol. 119, no. 351, DC2019-85, pp. 37-42, 2019-12.

[25] 加藤隆明, 三宅庸資, 梶原誠司, "オンチップ遅延測定における温度電圧影響の補正手法について," 第82回FTC研究会, 2020-01.

[26] 権藤昌之, 三宅庸資, 梶原誠司, "機械学習を用いたデジタル温度電圧センサの精度向上について," 電子情報通信学会技術研究報告, vol. 119, no. 420, DC2019-86, pp. 1-6, 2020-02.

[27] 三宅庸資, 梶原誠司, "フィールドテスト向けオンチップ遅延測定回路のIoT適用," 電子情報通信学会2020年総合大会論文集, D-10-5, p. 105, 2020-03.

[28] 森誠一郎, 権藤昌之, 三宅庸資, 加藤隆明, 梶原誠司, "勾配降下法を用いた回路遅延の劣化予測について," 電子情報通信学会技術研究報告, vol. 120, no. 288, DC2020-59, pp. 1-6, 2020年12月.

[29] 権藤昌之, 三宅庸資, 加藤隆明, 梶原誠司, "回路の動作状況の違いに伴う劣化予測モデル更新の有効性について," 電子情報通信学会2021年総合大会論文集, 情報・システム講演論文集1, D-10-3, p. 80, 2021-03.

その他(口頭発表)

[30] S. Kajihara, Y. Miyake, Y. Sato, "A Fully Digital Temperature and Voltage Sensor for IoT Devices," 5th International Symposium on Applied Engineering and Sciences (SAES2017), Selangor, Malaysia, Nov. 2017.[31] T. Nishimi, S. Kajihara, and Y. Nakamura, "Good Die Prediction Modeling from Specific Results of Wafer Tests," 2018 International Symposium on Dependable Integrated Systems, Jan. 2018.

[32] S. Oshima, T. Kato, S. Wang, Y. Sato, and S. Kajihara, "Flip-Flop Selection for Multi-Cycle Test with Partial Observation in Scan-Based Logic BIST," 2018 International Symposium on Dependable Integrated Systems, Jan. 2018.

[33] Seiji Kajihara, "A full digital temperature and voltage sensor for field testing," Conferences on CMOS Emerging Technologies 2018(ETCMOS2018), Canada, May 2018.

[34] 橘正意, 松浦宗寛, 三宅庸資, 加藤隆明, 梶原 誠司, "ブロックチェーンにおけるハッシュ関数のFPGA実装について," 2017年度第10回LSIテストセミナー, 福岡県福岡市, 2018年3月.

[35] 三宅庸資, "フィールドテストにおける劣化検出のためのオンチップ遅延測定," 九州工業大学 重点プロジェクトセンター合同ワークショップ, Oral Session, 福岡県北九州市, 2018-11.

[36] Masayuki Gondo, Yousuke Miyake, Seiji Kajihara, "On Machine Learning Based Calibration for An On-chip Digital Thermal/voltage Sensor," International Symposium on Applied Engineering and Sciences (SAES2019), Malaysia, Nov. 2019.

その他(ポスター発表)

[37] Masaki Hatae, Yousuke Miyake, Takaaki Kato, Yasuo Sato, and Seiji Kajihara, "On estimation formula of a digital temperature and voltage sensor for high accuracy," International Joint Workshop on Kyutech Research Centers, Poster Session, 2018-11.[38] Shigeyuki Oshima, Takaaki Kato, Yasuo Sato, Seiji Kajihara, and Senling Wang, "Multi-Cycle Scan Test with Partial Observation in Logic BIST," International Joint Workshop on Kyutech Research Centers, Poster Session, 2018-11.

[39] Takeru Nishimi, Seiji Kajihara, Yasuo Sato, and Yoshiyuki Nakamura, "Good Die Prediction Modeling from Limited Test Items," International Joint Workshop on Kyutech Research Centers, Poster Session, 2018-11.

[40] 麻生正雄, 二見治司, 松永恵士, 梶原誠司, 三宅庸資, 加藤隆明, 三浦幸也, "AIチップの高信頼を実現するオンチップ遅延劣化検出技術," LSIとシステムのワークショップ2019, Poster Session, May 2019.

その他(展示会出展)

[41] 三宅庸資, "デジタル温度電圧センサ技術," 九州カーエレクトロニクス展示商談会in刈谷(主催者:九州自動車・二輪車産業振興会議), 愛知県刈谷市, 2019-02.連絡先

詳細は梶原にご連絡ください(メールアドレスはMember)

Copyright(C) 2021 Kajihara, Wen, Miyase and Holst Lab. , All rights reserved.